機(jī)器人多軸控制同步性挑戰(zhàn)如何解決���?

目前工業(yè)機(jī)器人的發(fā)展趨勢(shì)一是協(xié)作,二是多軸�。所謂機(jī)器人的多軸驅(qū)控,即機(jī)器人在運(yùn)行時(shí)需要準(zhǔn)確地把控每一個(gè)軸的移動(dòng)�����。多軸機(jī)器人意味著有更多的自由度����,完成幾乎任何角度和軌跡的運(yùn)動(dòng)作業(yè)�。6軸機(jī)器人是目前工業(yè)機(jī)器人應(yīng)用里最為普遍的,如果應(yīng)用場(chǎng)景需要工業(yè)機(jī)器人能夠躲避特定的目標(biāo)���,那么就會(huì)再多出一個(gè)軸����,一般稱這種軸為冗余軸�����。

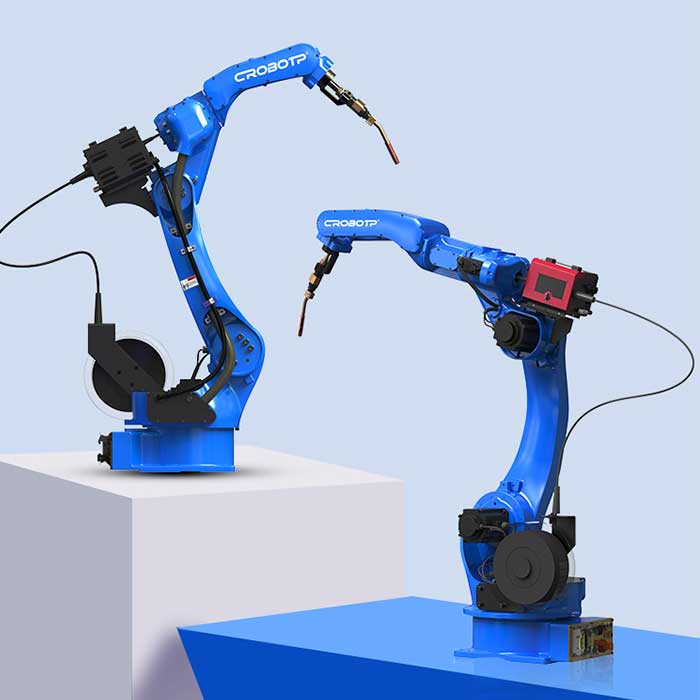

鄭州北元-多關(guān)節(jié)焊接機(jī)器人

在機(jī)器人的每一個(gè)軸中���,伺服驅(qū)動(dòng)和電機(jī)肯定是少不了的����。每個(gè)軸通過(guò)工業(yè)以太網(wǎng)互聯(lián),控制系統(tǒng)要將運(yùn)動(dòng)需要的空間軌跡轉(zhuǎn)換為每個(gè)伺服軸所需的單個(gè)位置基準(zhǔn)�,然后循環(huán)傳輸給每個(gè)機(jī)器軸。這些步驟一般會(huì)按照底層伺服電機(jī)驅(qū)動(dòng)的PWM時(shí)間周期來(lái)進(jìn)行����。在每一個(gè)時(shí)間周期內(nèi),或者說(shuō)控制周期內(nèi)���,位置的發(fā)送就會(huì)涉及軸到軸的網(wǎng)絡(luò)傳輸��。

此時(shí)挑戰(zhàn)出現(xiàn)了��,運(yùn)動(dòng)數(shù)據(jù)的傳輸延遲幾乎決定了工業(yè)機(jī)器人的同步性���,傳輸?shù)难舆t成了影響機(jī)器人多軸協(xié)同的重要參數(shù)。

在我們此前討論工業(yè)機(jī)器人連接器的文章中���,可以看到目前應(yīng)用于工業(yè)機(jī)器人的高性能連接線纜對(duì)信號(hào)傳輸?shù)哪芰σ呀?jīng)足夠強(qiáng)�,因此在這個(gè)挑戰(zhàn)中我們可以忽略連接線纜帶來(lái)的延遲�,那么剩下的就是數(shù)據(jù)傳輸?shù)骄€路延遲。這些延遲主要集中帶寬以及PHY上���。多軸機(jī)器人系統(tǒng)內(nèi)節(jié)點(diǎn)越多�����,此類延遲將不可避免地變大�����。

提高帶寬還是降低PHY延遲�?

通過(guò)低延遲PHY縮短網(wǎng)絡(luò)周期時(shí)間是最為直接的應(yīng)對(duì)此挑戰(zhàn)的方法���,盡可能在物理層設(shè)備上縮短PHY的延遲將大幅縮短網(wǎng)絡(luò)周期時(shí)間(控制器收集和更新所連器件的數(shù)據(jù)所需的時(shí)間)��。這種方法會(huì)改善網(wǎng)絡(luò)更新時(shí)間�����,對(duì)于多軸機(jī)器人這種需要對(duì)控制周期時(shí)間嚴(yán)格把控的應(yīng)用這一點(diǎn)至關(guān)重要��,這意味著每個(gè)周期網(wǎng)絡(luò)內(nèi)可以將更多器件連接到網(wǎng)絡(luò)���。這不是說(shuō)帶寬延遲并不重要,而是在帶寬已經(jīng)滿足數(shù)據(jù)吞吐量的情況下���,一味拔高帶寬會(huì)適得其反��。

以ADI在多軸機(jī)器人上應(yīng)用最多的PHY ADIN1300作為收發(fā)器�,假設(shè)接收緩沖器分析是以目標(biāo)地址為基礎(chǔ),且采用100 Mbps網(wǎng)絡(luò)�,1000BASE-T RGMI延遲發(fā)射< 68 ns,接收< 226 ns����,100BASE-TX MII延遲發(fā)射< 52 ns,接收< 248 ns�����,這個(gè)標(biāo)準(zhǔn)是屬于多軸系統(tǒng)完全接受的較低的延遲水平(根據(jù)具體的傳輸協(xié)議延遲會(huì)有些許差異)�����。

當(dāng)然也可以使用1 Gbps的傳輸網(wǎng)絡(luò)��,但帶寬的增加雖然能很明顯地減少低帶寬延遲帶來(lái)的影響���,但這不可避免地會(huì)增加開(kāi)關(guān)和PHY組件導(dǎo)致的總體延遲的比例���,導(dǎo)致留給下一周期更新電機(jī)控制和移動(dòng)控制算法計(jì)算的時(shí)間反而會(huì)減少�。確保帶寬肯定是必要的���,只不過(guò)帶寬足夠情況下降低PHY延遲是更能提升多軸系統(tǒng)同步性的辦法�����。

這類低延遲的以太網(wǎng)PHY往往集成相關(guān)的通用模擬電路���、輸入和輸出時(shí)鐘緩沖、管理接口和子系統(tǒng)寄存器以及MAC接口和控制邏輯�����,以便管理復(fù)位和時(shí)鐘控制以及引腳配置���。MII管理接口最好能在主機(jī)處理器和PHY器件之間提供雙線式串行接口,以便訪問(wèn)PHY內(nèi)核管理寄存器中的控制和狀態(tài)信息���。一般來(lái)說(shuō)PHY器件對(duì)電纜的支持會(huì)遠(yuǎn)超多軸機(jī)器人對(duì)線纜的需求����,就不必?fù)?dān)心此類問(wèn)題了����。

抗擾度成攔路虎

多軸機(jī)器人的工作環(huán)境雖然稱不上惡劣����,但很多應(yīng)用中場(chǎng)景要求都足夠嚴(yán)苛����。PHY器件要么會(huì)直接連接至電纜,要么會(huì)通過(guò)小型磁性元件連接至電纜���,這些連接可能帶來(lái)輻射和傳導(dǎo)干擾�����,嚴(yán)重影響傳輸延遲�����,所以PHY器件必須在抗擾度上跨過(guò)難關(guān)����。IEC 61000-4-2等EMC標(biāo)準(zhǔn)都可以作為衡量PHY的標(biāo)準(zhǔn)����。

目前較為領(lǐng)先的是PHY提供通過(guò)帶有非屏蔽/屏蔽功能的單雙絞線傳輸和接收數(shù)據(jù)所需的所有物理層功能�����。

優(yōu)化抗擾度意味著要有大量的實(shí)時(shí)監(jiān)控��、調(diào)試和器件測(cè)試�����。集成靜電放電(ESD)監(jiān)測(cè)肯定是少不了的�,任何ESD保護(hù)都離不開(kāi)這個(gè)功能�,它能夠計(jì)算xMII和MDI上的ESD事件,并通過(guò)使用可編程中斷提供實(shí)時(shí)監(jiān)控����。此外,為了提升整體系統(tǒng)的低延遲下高穩(wěn)定性��,各類保護(hù)功能都會(huì)被集成進(jìn)芯片中�。有的芯片廠商還給出了集成了一個(gè)數(shù)據(jù)生成器的辦法����,用于生成可定制的MAC數(shù)據(jù)包,并檢查傳入數(shù)據(jù)包上的錯(cuò)誤�����,這使得系統(tǒng)級(jí)數(shù)據(jù)路徑測(cè)試/優(yōu)化不依賴于MAC,大大提升了系統(tǒng)的可靠性�。不能提供穩(wěn)定的低延遲那么多軸機(jī)器人的同步性就大打折扣。

PHY損耗同樣不可忽視

多軸機(jī)器人所需的器件通常采用IP65/IP66等級(jí)的保護(hù)����,高溫也是工業(yè)設(shè)備都要面對(duì)的問(wèn)題。不僅如此�,多個(gè)以太網(wǎng)連接也會(huì)使得數(shù)據(jù)輸入和輸出相關(guān)的PHY損耗翻倍。所以降低PHY損耗以此來(lái)降低器件的自發(fā)熱也是應(yīng)對(duì)多軸機(jī)器人控制不能忽視的一點(diǎn)�����。